### CMB-S4

#### contribution to the front-end readout chain

### Damien PRÊLE

on behalf of the CMB-S4@IN2P3: Horacio Arnaldi<sup>(1)</sup>, James Bartlett <sup>(1)</sup>, Olivier Bourrion<sup>(4)</sup>, Andrea Catalano<sup>(4)</sup>, **Si Chen** <sup>(1)</sup>, Céline Combet<sup>(4)</sup>, Jacques Delabrouille<sup>(2)</sup>, Elena de laHoz<sup>(2)</sup>, Cyrille Doux<sup>(4)</sup>, Josquin Errard<sup>(1)</sup>, Ken Ganga<sup>(1)</sup>, Xavier Garrido<sup>(3)</sup>, **Manuel Gonzalez**<sup>(1)</sup>, Jean-Christophe Hamilton<sup>(1)</sup>, Sophie Henrot-Versillé<sup>(3)</sup>, Julius Hrivnac<sup>(3)</sup>, Marine Kuna<sup>(4)</sup>, Fabian Lambert<sup>(4)</sup>, Sotiris Loucatos<sup>(1)</sup>, Thibaut Louis<sup>(3)</sup>, Juan Macías Pérez<sup>(4)</sup>, Frédéric Mayet<sup>(4)</sup>, Jerôme Odier<sup>(4)</sup>, Julien Peloton<sup>(4)</sup>, Laurence Perotto<sup>(4)</sup>, **Michel Piat**<sup>(1)</sup>, **Damien Prêle**<sup>(1)</sup>, **Fatah Rarbi**<sup>(4)</sup>, Radek Stompor<sup>(2)</sup>, Jean-Pierre Thermeau<sup>(1)</sup>, Steve Torchinsky<sup>(1)</sup>, Matthieu Tristram<sup>(3)</sup>, Christophe Vescovi<sup>(4)</sup>

- (1) AstroParticule et Cosmologie (APC)

- (2) Centre Pierre Binétruy (CPB)

- (3) Laboratoire de Physique de 2 infinis, Iréne Joliot-Curie, (IJCLab)

- (4) Laboratoire de Physique Subatomique et Cosmologie, (LPSC)

#### Who Am I

### Damien PRÊLE - APC / Univ. Paris Cité

### CMB-S4 project and collaboration member

- Instrumentalist for the QUBIC ground based telescope for CMB

- Project manager Warm Front End Electronic WFEE for X-IFU ATHENA

- Co-Investigator member of the X-IFU instrument

- ATHENA X-IFU detection chain WG

- IN2P3 instrument leader CMB S4 warm analog front-end readout

- CMB-S4 readout chain WG

Micro-electronic and BiCMOS SiGe integrated circuits – ASIC, Cryo. Semiconductors, Superconductor devices (SQUID, TES), Electronic Noise mitigations and EMI/EMC, Multiplexing, Low noise amplifier – LNA, Low noise DACs, Space technology

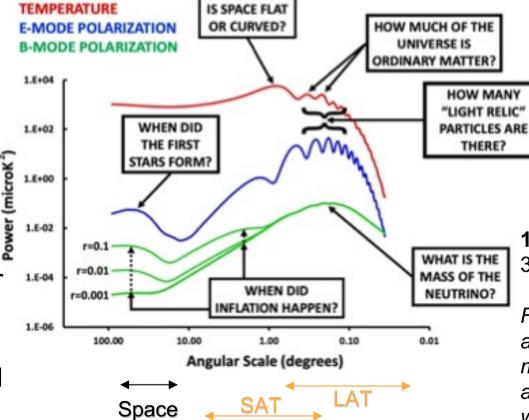

# **CMB Angular Power Spectra Guide**

Weak anisotropy

Encoded in CMB

intensity and

polarization -> story of

the origin, evolution,

and make up of the

Universe.

Need to measure the anisotropy from angular scales of **degrees to** arcminutes with exquisite sensitivity and fidelity.

**10nK fluctuations** on a 3K in a 300K environment

Foregrounds mitigation and de-lensing requires multiple frequency bands and broad angular range with exceptional sensitivity and control of systematics

CMB-S4 AstroCeNT 19/12/2023

John Carlstrom

**CMB-S4 Instrument Description after AoA**

- **500** k deployed detectors (483344)

- 363 wafers (All wafers are dichroic except the ULF wafer)

- 3 LATs

- 2 x 6 m CD\* Chile > 50% sky

- 1 x 5 m TMA\*\* Pole ~3% sky)

- -> 3x85 tubes<sub>20cm</sub>; 255 wafers; 400 k detectors

- 200 TES ULF; 5k LF; 280k MF; 120k HF

- 3 SATs

- -> 3x3 tubes<sub>50cm</sub>; 108 wafers; 80 k detectors

- 500 TES LF; 40k MF; 40k HF

2x CHLATs

**SATs**

**SPLAT**

## CMB-S4 LAT and SAT receiver cryostat design

1.3-m

~10,000 lbs

(4536 kg)

CeNT 19/12/2023

\*\*\* JLTP 2022 DOI: 10.1007/s10909-022-02731-x

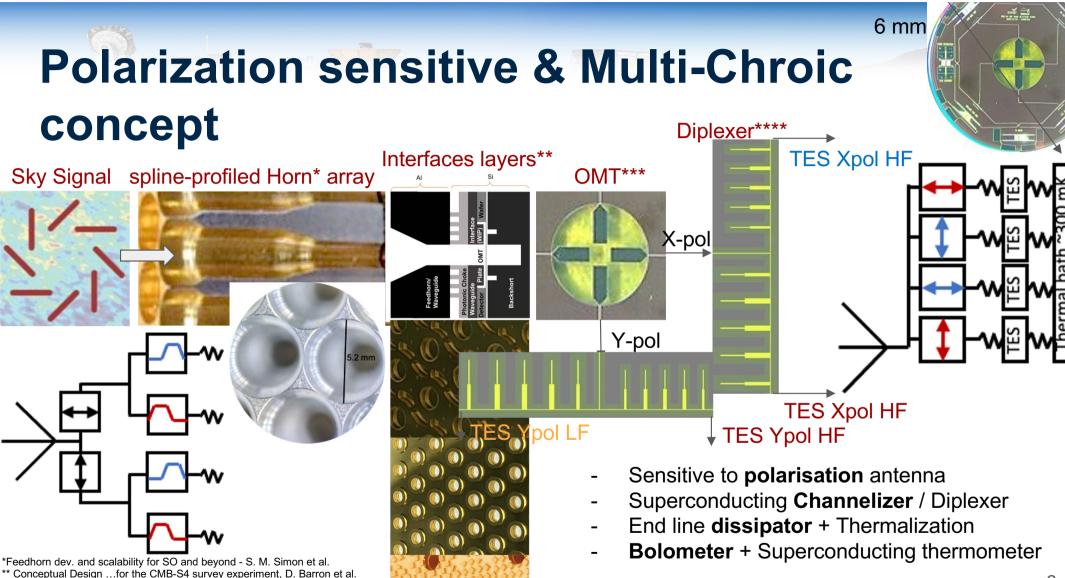

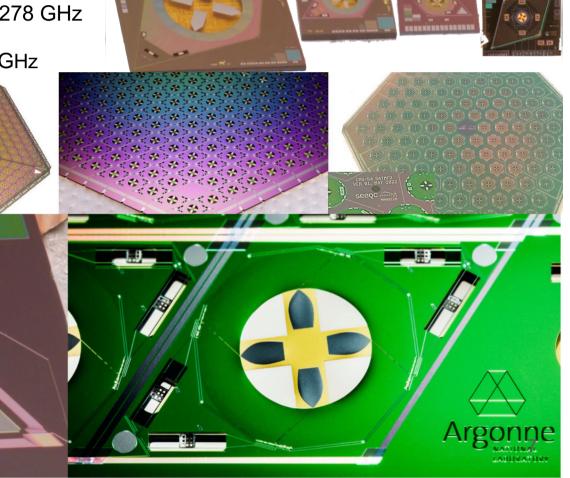

## TES: polarisation sensitive + multichroic

6 fabrication sites: NIST, Argonne, UCB, LBNL/SQC, JPL

**SAT**: 30/40 GHz, 85/145 GHz, 95/155 & GHz 225/278 GHz

**LAT**: 20 GHz, 30/40 GHz, 90/150 GHz & 225/278 GHz

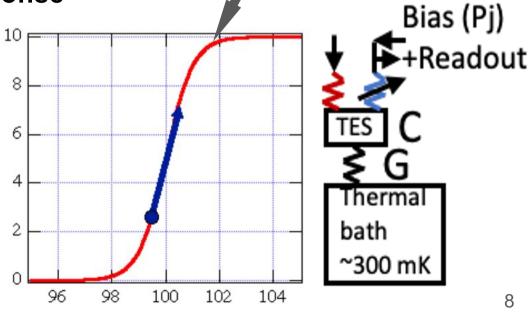

**Transition Edge Sensors**

Quadratic detection at the line end

- Bias dissipation  $\square$   $P_J = V_{bias}^2/R_{TES}$

• auto adjustment in an array @ Tc

• response homogenisation response

$\partial I_{TES}/\partial P_J = 1/V_{bias}$

Improve time response < C/G</li>

Strong Electro Thermal Feedback - ETF

Voltage biasing

= detection transfer function

300µm

Temperature [m K]

Readout + Pi

Ρi

G

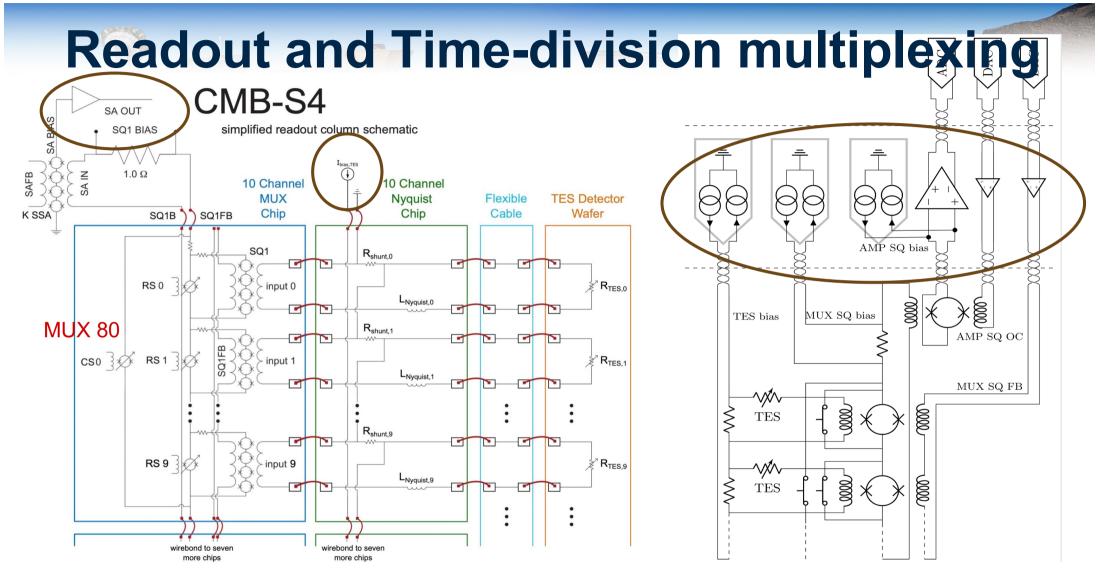

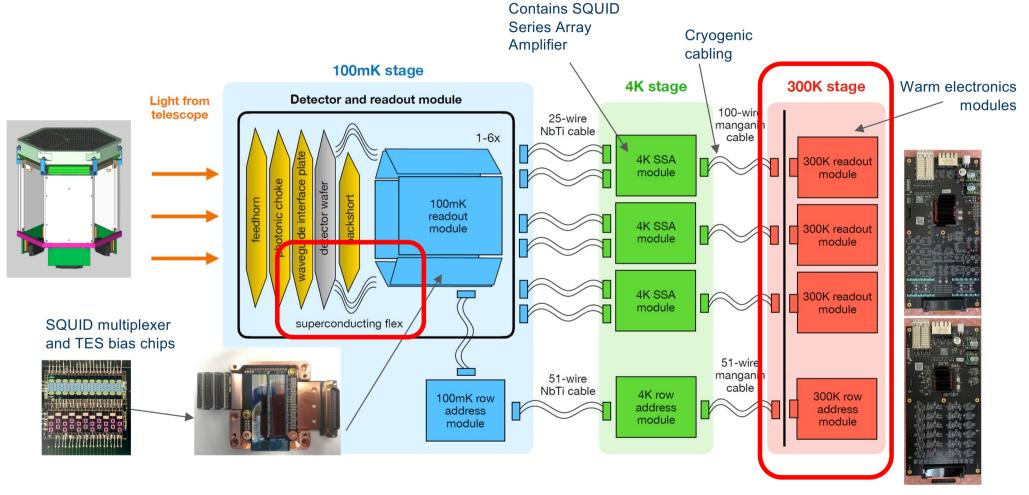

## Readout subsystem

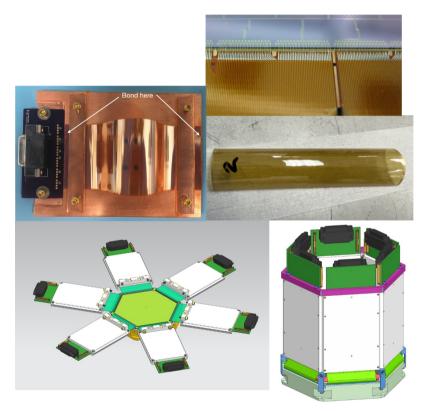

# Superconducting Flex

- Development led by CEA

- Production planned to be carried by two companies Hightec and Cicor/Microtech.

- Flexible

- Superconducting

- Low parasitic resistance ( $\ll 1 \text{m}\Omega$ )

- High yield (~100%)

Al assisted visual inspection tool to be developed

Cryogenic tests to be performed at APC/Cryo-MAT

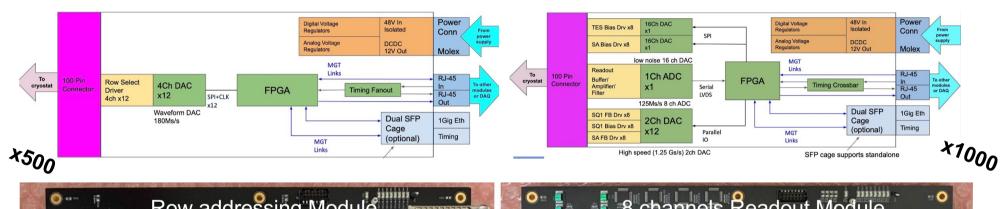

## Warm readout

### This subsystem is under SLAC responsibility

# Warm readout background

### Front-end readout ASIC family designed for ATHENA X-IFU

#### Specific Integrated Circuit for the X-IFU Warm Front-End Electronics

Damien Prêle (APC, Paris) on behalf of the WFEE and X-IFU detection chain team.

The X-IFU (X-ray Integral Field Unit) instrument of the Athena mission is designed to operate with 3168 superconducting microcalorimeters (read out by Transition Edge Sensors -TES) cooled to 50 mK, providing an imaging spectrometer for X-ray astronomy. The unprecedented spectral resolution of 2.5 eV up to 7 keV requires low noise readout electronics. Located immediately outside the cryostat, the Warm Front End Electronics (WFEE) is a key component of the readout electronics.

The WFEE amplifies the detection chain signal, adjusts the operating points of the cryogenic devices (Superconducting QUantum Interference Devices - SQUIDs), and feeds through the TES bias and feedback loop. Using Frequency Domain Multiplexing (FDM, see Athena Nugget #25 for more details), 40 microcalorimeters are read out per channel and 40 carriers between 1 to 5 MHz are injected to 40 sensors. As a result, the detected X-ray pulses are transposed into 40 different frequencies. Ultimately, about one hundred channels are needed for the full readout of the TES array.

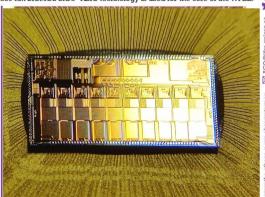

To meet the energy resolution of the cryogenic sensors, the WFEE, like the whole readout chain, has to exhibit ultra-low noise and extremely small gain-drift. At the same time, the size, the mass, and the dissipation must be minimized as required for a space mission. For this reason, an Application-Specific Integrated Circuit (ASIC) has been designed for the WFEE. "350 nm BiCMOS SiGE" ASIC technology is used for the Core to the WFEE.

"350nm" corresponds to the minimum gate size of MOS transistors. "BiCMOS" means that both bipolar transistors and complementary (N and P) MOS transistors can be built using this technology. Finally, "SiGe" indicates that Silicon-Germanium alloy is used to make the base-emitter junction of the bipolar transistor. Such a hetero-junction increases the speed of the transistors allowing the design of a wide-band amplifier covering the frequency range of the carriers used for the FDM. The micro-photograph illustrates an ASIC chip design for the WFEE. Eight independent readout channels will be integrated on a chip of one square centimetre.

The noise degradation of WFEE is minimized by reducing any parasitic resistance and thanks to fine-tuning of the transistors biasing to operate in an optimal noise condition.

The gain drift is also a significant contributor to the energy resolution budget. At large time scale (> 1s), the thermal drift is the main cause of electronic parameter shifts. The entire circuit is based on a specific design including thermal compensation techniques.

The WFEE with its custom designed ASIC is a compact, light-weight component with minimal power consumption and it delivers the high performance required for Athena's X-IFU readout electronics.

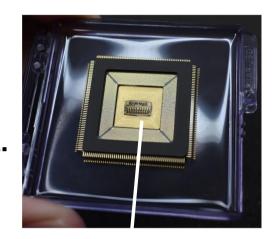

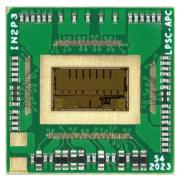

# Front-end readout daughter board

Drop-in integrated circuit for analog readout.

Bias and amplification for 2 TDM columns.

Initially developed for X-ray TES readout (ATHENA)

Fully differential, low noise and low thermal drift.

Daughter board based on current package

- Fabricated

- Delivered last week

- First tests/adjustments currently done

2 x LNA 20 MHz 0.7 nV/√Hz 2 x DC DAC for SQ1 bias 2 x DC DAC for SSA bias 2 x DC DAC for TES bias DACs controlled through I2C

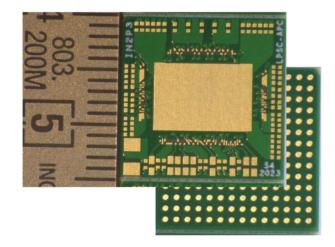

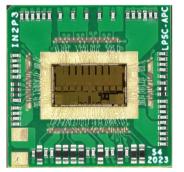

# Design of new compact BGA package

1.5 cm PCB with glued and bonded ASIC naked die and passive components

**Compact system in package** of the ASIC as a BGA\* In preparation for 4 ASICs integration in one board

\*Ball Grid Array - BGA: chip carrier, surface-mount packaging

| Company                                 | Work                                 | Delay   |

|-----------------------------------------|--------------------------------------|---------|

| PCB electronics<br>(french<br>company)  | PCB Fabrication                      | 4 weeks |

| LPC Clermont-<br>Ferrand (IN2P3<br>Lab) | Soldering -<br>Passive<br>components | 2 weeks |

| C4PI @IPHC<br>(IN2P3 Lab)               | wire bonding -<br>Chip on Board      | 2 weeks |

| Itancia                                 | Solder Bump                          | 6 weeks |

15

### CMB-S4 Task Order / IN2P3 - CRADA

Task/Milestone

Work Done

**Execution Period to Completion**

- Objectives identified in a CRADA

- Real ongoing collaboration with SLAC

- First hardware produced in December 2023

- B. Design, development, and deployment of components an management subsystem WBS 1.09:

- 1.09.02 Data Movement. Design, development, d operation of:

- Data registration system

- Data archiving system

- Data distribution system (specifically in distribution center is included in the pro

### 1.09.03 Software Infrastructure

- Data Model: DD&D of a metadata inter

- Software Deployment: system-specific workflows (specifically in the event the is included in the project scope)

- Workflow Execution: execution of da

- 1.09.04 Data Simulations. DD&D of: Software modules to simulate syste

- Software modules to simulate syste

- Validation & Verification systems

- o 1.09.05 Data Reduction. DD&D of: Systems to characterize the instru systematic effects) from the raw a

- Software modules to mitigate sys time-ordered data to well-charac

- Validation & Verification systems

#### ANNEX B CMB-S4 Task Order (HEREINAFTER "Project")

#### October 2023

This Task Order is subject to and governed by CRADA No. FP00006410 ("CRADA") between the Parties and all the terms, conditions, definitions, and provisions of said CRADA are hereby incorporated by reference. The Parties agree to perform their respective obligations related to this Project in accordance with the terms and conditions of this Task Order, Annex A (Master SOW) and other documents attached or Incorporated by reference, which together constitute the entire Task Order. In the event of any conflict between the provisions of this Task Order and the provisions of the CRADA, the CRADA shall control.

#### HOME INSTITUTION: IN2P3

HOST INSTITUTION: LBNL, as lead laboratory for the CMB-S4 Project.

PROJECT DESCRIPTION: Cosmic Microwave Background – Stage 4 (CMB-S4) Project

#### BACKGROUND

The Parties intend to work jointly toward fabricating and operating an instrument capable of meeting the CMB-S4 scientific requirements by participating in scientific and technical collaboration in the field of cosmic microwave background physics in support of the CMB-S4 Project areas. This Annex outlines the proposed collaboration between LBNL, as the lead laboratory for the CMB-S4 Project, and IN2P3. Work under this agreement may include visits and assignments to other U.S. institutions within the CMB-S4 Project, coordinated through

#### ESTIMATED PERIOD OF PERFORMANCE

The estimated Period of Performance of this Task Order is from October 1 2023, through September 30 2026. It is intended that joint work during the Project construction phase will be further clarified as the Project Performance Baseline is devel-

| Task Willestoffe |                                                                                                                              | By         |           | Quarters After Start start in October 1, 2023 |   |   |       |    |       |        |            |    |     |    |    |

|------------------|------------------------------------------------------------------------------------------------------------------------------|------------|-----------|-----------------------------------------------|---|---|-------|----|-------|--------|------------|----|-----|----|----|

|                  |                                                                                                                              | CMB<br>-S4 | IN2<br>P3 | 1                                             | 2 | 3 | 4     | 5  | 6     | 7      | 8          | 9  | 10  | 11 | 12 |

| R0-01            | ICD for ASICv3 2-channel integration with CMB-S4 front-end module for warm readout module                                    | X          | Х         | Х                                             |   |   | J. S. |    | - ATT | 550 Mg | - Tills    |    |     |    |    |

| R0-02            | Design/fab/bench-test<br>ASIC daughter board<br>with one ASICv3 (2                                                           |            | Х         |                                               | х | x | 4     |    |       |        | ×          |    |     |    |    |

| 7                | channels) in a<br>CQFP208                                                                                                    |            |           |                                               |   |   |       |    | 100   | 8888   | 100        |    |     |    |    |

| R0-03            | Modification<br>(design/fab/bench-tes<br>t) Front-End Board to<br>accept ASICv3<br>daughterboard                             | x          |           |                                               |   | x | x     | ir | ηp    | re     | <b>p</b> a | ar | ati | or | ח  |

| RO-04            | Performance testing<br>and analysis of<br>results for v3 in<br>CQFP208 package<br>on front-end module.                       | х          |           |                                               |   |   | x     | x  | S     | 00     | on         |    |     |    | 44 |

| R0-05            | Package 2-channel ASICv3 in a new smaller chip package. Update ASIC daughter board.                                          |            | х         |                                               | х | x | x     | х  |       |        |            |    |     |    |    |

| R0-06            | Performance testing<br>and analysis of<br>results for 2-channel<br>v3 in new smaller<br>chip package on<br>front-end module. | х          |           |                                               |   |   |       | х  | ×     |        |            |    |     |    |    |

| R0-07            | ICD for vS4 ASIC chip integration with CMB-S4 warm readout module                                                            | х          | х         |                                               |   |   |       | х  |       |        |            |    |     |    |    |

| R0-08            | Design, DOE/IN2P3<br>review, fab of<br>ASICvS4 chips,<br>supporting daughter<br>boards, pre-test                             |            | Х         |                                               |   |   |       |    | ×     | x      | x          | x  | X   |    |    |

| R0-09            | Modification of warm<br>readout module to<br>accept ASICvS4                                                                  | х          |           |                                               |   |   |       |    |       |        |            | х  | x   | х  |    |

|                  | daughter board                                                                                                               |            |           |                                               |   |   |       |    |       |        |            |    |     |    |    |

| R0-10            | Performance testing and analysis for vS4                                                                                     | х          |           |                                               |   |   |       |    |       |        |            |    |     | х  | х  |

|                  |                                                                                                                              |            |           |                                               |   |   |       |    |       |        |            |    |     |    |    |

#### TECHNICAL OBJECTIVES

The Parties intend to collaborate to develop designs systems to validate conceptual and preliminary desi-

# Conclusions and way forward

- Strong interest of the CMB community on the CMB-S4 science and instrumental developments

- Readout contributions/activities for the next three years formalized

- Cohesive effort to capitalize the development for other CMB projects

- Strong collaboration with SLAC

- First French CMB-S4 hardware delivered last week

- We need to start thinking about the production phase